服務熱線

0755-83044319

發布時間:2022-03-17作者來源:薩科微瀏覽:3861

導 讀

Suny Li ~1

首先,我們想請Swan院士談一談 Intel 在先進封裝技術領域的研發規劃和 [敏感詞]的研究成果。Johanna Swan ~1

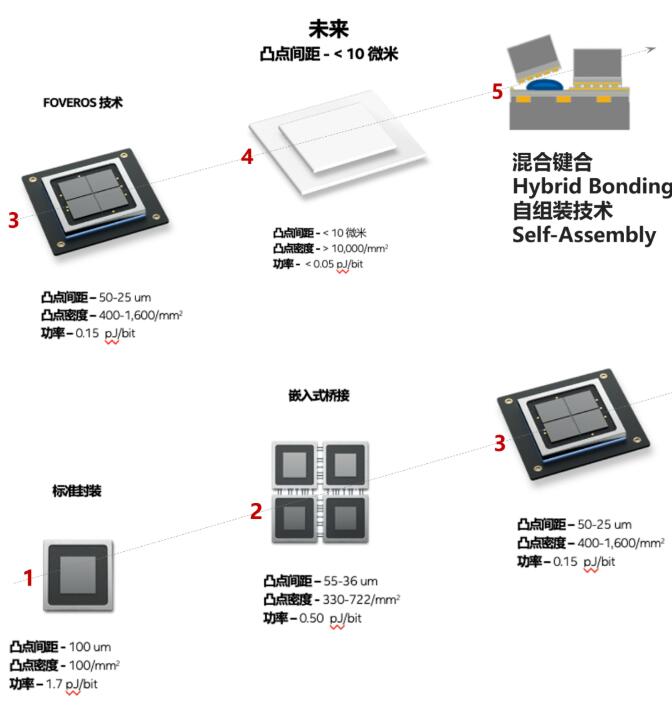

好的 ,我首先給大家分享 Intel 先進封裝技術路線圖,圖中 X 軸代表功率效率, Y 軸代表互連密度,Z 軸則展示了我們的技術可擴展性。

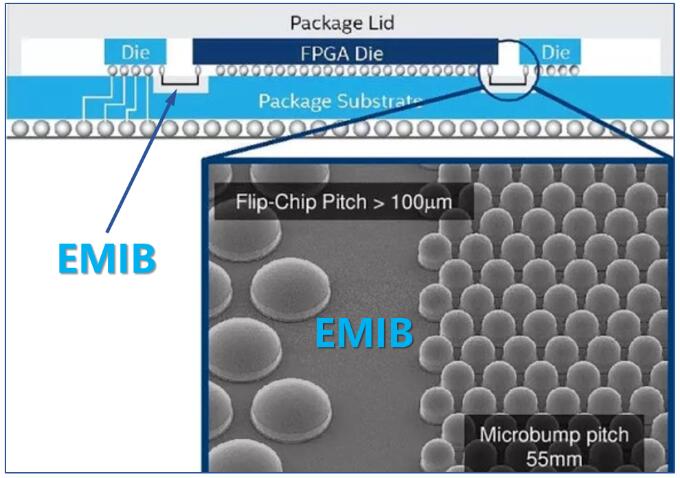

從標準封裝,到嵌入式多芯片互聯橋EMIB,更多的芯片被包含到封裝中,凸點間距也越來越小,從100um變為55-36um。

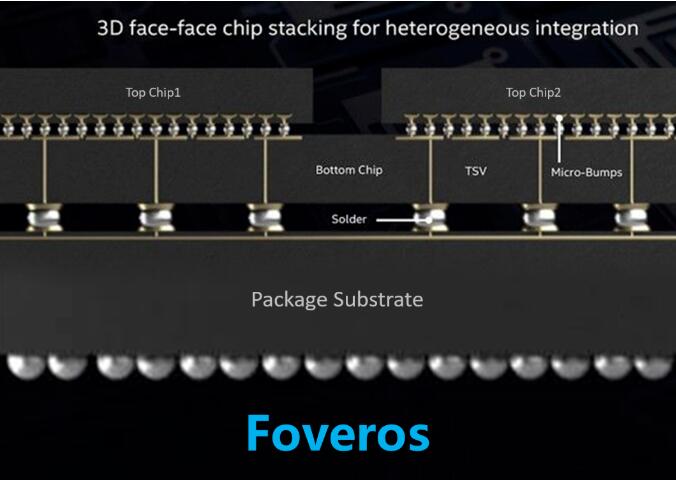

在今年 ECTC 上 Intel 發表了一篇關于混合鍵合技術的論文,這是一種在相互堆疊的芯片之間獲得更密集互連的方法,并可實現更小的外形尺寸。下圖左邊的技術,被稱為 Foveros,凸點間距是 50 微米,每平方毫米有大約 400 個凸點。對于未來, Intel 要做的是縮減到大約 10 微米的凸點間距,并達到每平方毫米 10,000 個凸點。

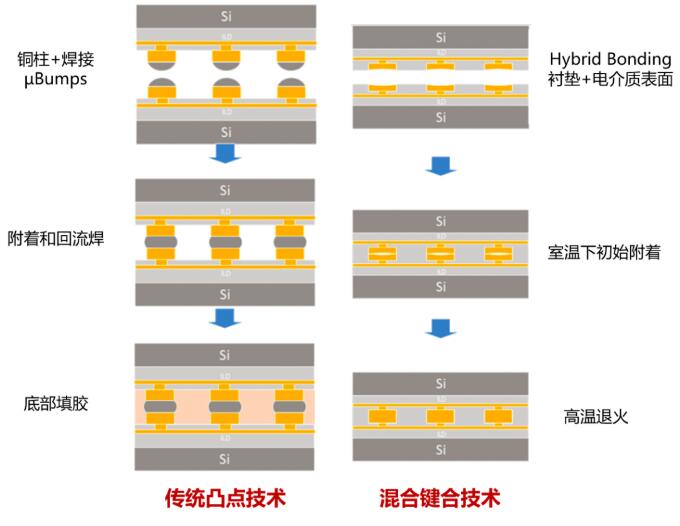

Hybrid Bonding 技術可以在芯片之間實現更多的互連,并帶來更低的電容,降低每個通道的功率,并讓我們朝著提供[敏感詞]產品的方向發展。

下圖是傳統凸點焊接技術和Hybrid Bonding 混合鍵合技術的比較,混合鍵合技術需要新的制造、操作、清潔和測試方法。混合鍵合技術的優勢包括:有更高的電流負載能力,可擴展的間距小于1微米,并且具有更好的熱性能。

Chiplet 技術改變了芯片到芯片的互聯, 更多的芯片間互聯需要更高的互聯密度,因此需要從傳統的凸點焊接轉向混合鍵合。

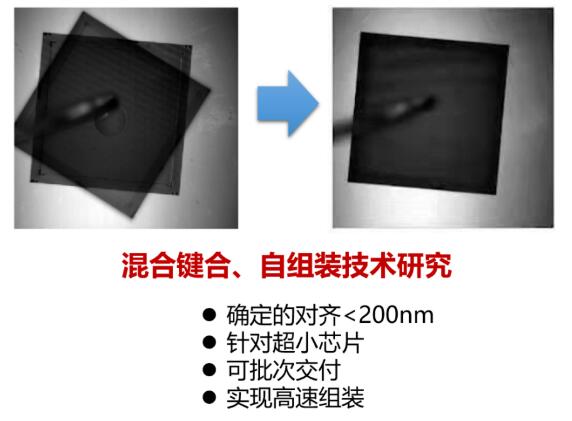

此外,我們面對另一個挑戰,就是如何將這些芯片組裝到一起,并保持制造流程以相同的速度進行。現在有更多的芯片需要放置,能否在一次只放置一個芯片的基礎上以足夠快的速度加工?解決方案是批量組裝,我們稱之為自組裝Self-Assembly技術。

Intel 正在積極與法國原子能委員會電子與信息技術實驗室 CEA-LETI 合作,研究一次能夠放置多個芯片,同時進行確定性快速放置,拾取并放置更多芯片。

免責聲明:本文轉載自“SiP與先進封裝技術”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:[email protected]

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號